新書推薦:

《

梁思永夏鼐往还书札

》

售價:NT$

653

《

【清华豆包AI全场景应用】豆包全场景应用:豆包+即梦+剪映+海绵音乐+扣子智能体

》

售價:NT$

356

《

17~20世纪西藏佛教造像艺术研究

》

售價:NT$

806

《

索恩丛书·狂暴:麦克阿瑟、山下奉文和马尼拉之战

》

售價:NT$

709

《

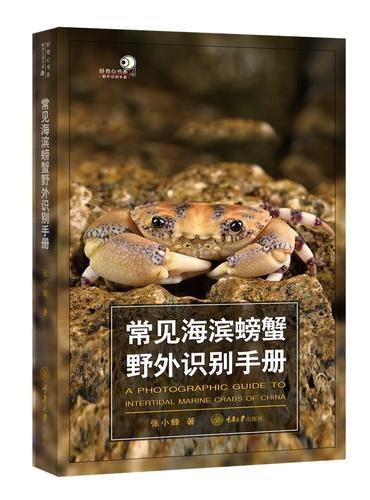

常见海滨螃蟹野外识别手册

》

售價:NT$

301

《

解码中国健康: 居民健康社会影响因素的实证探索

》

售價:NT$

500

《

如何让孩子自主学习

》

售價:NT$

305

《

魏晋南北朝史论丛(精)——中华学术·有道

》

售價:NT$

439

|

| 內容簡介: |

|

本书是作者在已经出版的 《Xilinx Zynq-7000嵌入式系统设计与实现:基于ARM Cortex-A9双核处理器和Vivado的设计方法》 一书的基础上进行修订而成的。 本书新修订后内容增加到30章。修订后,本书的一大特色就是加入了Arm架构及分类、使用PetaLinux工具在Zynq-7000 SoC上搭建Ubuntu操作系统,以及在Ubuntu操作系统环境下搭建Python语言开发环境,并使用Python语言开发应用程序的内容。本书修订后。进一步降低了读者学习Arm Cortex-A9嵌入式系统的门槛,并引入了在Zynq-7000 SoC上搭建Ubuntu操作系统的新方法。此外,将流行的Python语言引入到Arm嵌入式系统中,进一步拓宽了在Arm嵌入式系统上开发应用程序的方法。

|

| 關於作者: |

|

著名的嵌入式技术和EDA技术专家,长期从事电子设计自动化方面的教学和科研工作,与全球多家知名的半导体厂商和EDA工具厂商大学计划保持紧密合作。目前已经出版嵌入式和EDA方面的著作近60部,内容涵盖电路仿真、电路设计、可编程逻辑器件、数字信号处理、单片机、嵌入式系统、片上可编程系统等。典型的代表作有《Xilinx FPGA设计权威指南》、《Altium Designer13.0电路设计、仿真与验证权威指南》、《Xilinx FPGA数字设计:从门级到行为级的双重描述》、《Xilinx FPGA数字信号处理权威指南:从HDL、模型到C的描述》、《STC单片机原理及应用》、《Altium Designer15.0电路仿真、设计、验证与工艺实现权威指南》、《STC单片机C语言程序设计》、《Cypress WICED物联网开发指南:从传感器、无线接入到云端的设计与实现》,以及《模拟电子系统设计指南(基础篇):从半导体、分立元件到ADI集成电路的分析与实现》。

|

| 目錄:

|

目 录

第 章 Zynq - 7000 SoC设计导论 1

1.1 全可编程片上系统基础知识 1

1.1.1 全可编程片上系统的演进 1

1.1.2 SoC与MCU和CPU的比较 3

1.1.3 全可编程SoC诞生的背景 4

1.1.4 可编程SoC系统技术特点 5

1.1.5 全可编程片上系统中的处理器类型 5

1.2 Arm架构及分类 6

1.2.1 M - Profile 7

1.2.2 R - Profile 9

1.2.3 A - Profile 10

1.3 Zynq - 7000 SoC功能和结构 11

1.3.1 Zynq - 7000 SoC产品分类及资源 12

1.3.2 Zynq - 7000 SoC的功能 12

1.3.3 Zynq - 7000 SoC处理系统PS的构成 14

1.3.4 Zynq - 7000 SoC可编程逻辑PL的构成 19

1.3.5 Zynq - 7000 SoC内的互联结构 20

1.3.6 Zynq - 7000 SoC的供电引脚 22

1.3.7 Zynq - 7000 SoC内MIO到EMIO的连接 23

1.3.8 Zynq - 7000 SoC内为PL分配的信号 28

1.4 Zynq - 7000 SoC在嵌入式系统中的优势 30

1.4.1 使用PL实现软件算法 30

1.4.2 降低功耗 32

1.4.3 实时减负 33

1.4.4 可重配置计算 34

第 章 AMBA规范 35

2.1 AMBA规范及发展 35

2.1.1 AMBA 1 36

2.1.2 AMBA 2 36

2.1.3 AMBA 3 36

2.1.4 AMBA 4 37

2.1.5 AMBA 5 38

2.2 AMBA APB规范 40

2.2.1 AMBA APB写传输 40

2.2.2 AMBA APB读传输 42

2.2.3 AMBA APB错误响应 43

2.2.4 操作状态 44

2.2.5 AMBA 3 APB信号 44

2.3 AMBA AHB规范 45

2.3.1 AMBA AHB结构 45

2.3.2 AMBA AHB操作 46

2.3.3 AMBA AHB传输类型 48

2.3.4 AMBA AHB猝发操作 50

2.3.5 AMBA AHB传输控制信号 53

2.3.6 AMBA AHB地址译码 54

2.3.7 AMBA AHB从设备传输响应 55

2.3.8 AMBA AHB数据总线 58

2.3.9 AMBA AHB传输仲裁 59

2.3.10 AMBA AHB分割传输 64

2.3.11 AMBA AHB复位 67

2.3.12 关于AHB数据总线的位宽 67

2.3.13 AMBA AHB接口设备 68

2.4 AMBA AXI4规范 69

2.4.1 AMBA AXI4概述 69

2.4.2 AMBA AXI4功能 70

2.4.3 AMBA AXI4互联结构 78

2.4.4 AXI4 - Lite功能 79

2.4.5 AXI4 - Stream功能 80

第 章 Zynq - 7000系统公共资源及特性 83

3.1 时钟子系统 83

3.1.1 时钟子系统架构 83

3.1.2 CPU时钟域 84

3.1.3 时钟编程实例 86

3.1.4 时钟子系统内的生成电路结构 87

3.2 复位子系统 91

3.2.1 复位子系统结构和层次 92

3.2.2 复位流程 93

3.2.3 复位的结果 94

第 章 Zynq调试和测试子系统 95

4.1 JTAG和DAP子系统 95

4.1.1 JTAG和DAP子系统功能 97

4.1.2 JTAG和DAP子系统IO信号 99

4.1.3 编程模型 99

4.1.4 Arm DAP控制器 101

4.1.5 跟踪端口接口单元(TPIU) 102

4.1.6 Xilinx TAP控制器 102

4.2 CoreSight系统结构及功能 103

4.2.1 CoreSight结构概述 103

4.2.2 CoreSight系统功能 104

第 章 Cortex - A9处理器及指令集 107

5.1 应用处理单元概述 107

5.1.1 基本功能 107

5.1.2 系统级视图 108

5.2 Cortex - A9处理器结构 110

5.2.1 处理器模式 111

5.2.2 寄存器 113

5.2.3 流水线 118

5.2.4 分支预测 118

5.2.5 指令和数据对齐 119

5.2.6 跟踪和调试 121

5.3 Cortex - A9处理器指令集 122

5.3.1 指令集基础 122

5.3.2 数据处理操作 125

5.3.3 存储器指令 130

5.3.4 分支 131

5.3.5 饱和算术 133

5.3.6 杂项指令 134

第 章 Cortex - A9片上存储器系统结构和功能 138

6.1 L1高速缓存 138

6.1.1 高速缓存背景 138

6.1.2 高速缓存的优势和问题 139

6.1.3 存储器层次 140

6.1.4 高速缓存结构 140

6.1.5 缓存策略 145

6.1.6 写和取缓冲区 147

6.1.7 缓存性能和命中速度 147

6.1.8 无效和清除缓存 147

6.1.9 一致性点和统一性点 149

6.1.10 Zynq - 7000中Cortex - A9 L1高速缓存的特性 151

6.2 存储器顺序 153

6.2.1 普通、设备和强顺序存储器模型 154

6.2.2 存储器属性 155

6.2.3 存储器屏障 155

6.3 存储器管理单元 159

6.3.1 MMU功能描述 160

6.3.2 虚拟存储器 161

6.3.3 转换表 162

6.3.4 页表入口域的描述 165

6.3.5 TLB构成 167

6.3.6 存储器访问顺序 169

6.4 侦听控制单元 170

6.4.1 地址过滤 171

6.4.2 SCU主设备端口 171

6.5 L2高速缓存 171

6.5.1 互斥L2 - L1高速缓存配置 173

6.5.2 高速缓存替换策略 174

6.5.3 高速缓存锁定 174

6.5.4 使能禁止L2高速缓存控制器 176

6.5.5 RAM访问延迟控制 176

6.5.6 保存缓冲区操作 176

6.5.7 在Cortex - A9和L2控制器之间的优化 177

6.5.8 预取操作 178

6.5.9 编程模型 179

6.6 片上存储器 180

6.6.1 片上存储器概述 180

6.6.2 片上存储器功能 181

6.7 系统地址分配 186

6.7.1 地址映射 186

6.7.2 系统总线主设备 188

6.7.3 IO外设 188

6.7.4 SMC存储器 188

6.7.5 SLCR寄存器 188

6.7.6 杂项PS寄存器 189

6.7.7 CPU私有寄存器 189

第 章 Zynq - 7000 SoC的Vivado基本设计流程 190

7.1 创建新的工程 190

7.2 使用IP集成器创建处理器系统 192

7.3 生成顶层HDL并导出设计到SDK 197

7.4 创建应用测试程序 199

7.5 设计验证 202

7.5.1 验证前的硬件平台准备 202

7.5.2 设计验证的具体实现 203

7.6 SDK调试工具的使用 205

7.6.1 打开前面的设计工程 205

7.6.2 导入工程到SDK 205

7.6.3 建立新的存储器测试工程 205

7.6.4 运行存储器测试工程 206

7.6.5 调试存储器测试工程 207

7.7 SDK性能分析工具 209

第 章 Arm GPIO的原理和控制实现 213

8.1 GPIO模块原理 213

8.1.1 GPIO接口及功能 214

8.1.2 GPIO编程流程 217

8.1.3 IO接口 218

8.1.4 部分寄存器说明 218

8.1.5 底层读写函数说明 220

8.1.6 GPIO的API函数说明 220

8.2 Vivado环境下MIO读写控制的实现 221

8.2.1 调用底层读写函数编写GPIO应用程序 221

8.2.2 调用API函数编写控制GPIO应用程序 224

8.3 Vivado环境下EMIO读写控制的实现 226

8.3.1 调用底层读写函数编写GPIO应用程序 227

8.3.2 调用API函数编写控制GPIO应用程序 232

第 章 Cortex - A9异常与中断原理及实现 236

9.1 异常原理 236

9.1.1 异常类型 237

9.1.2 异常处理 241

9.1.3 其他异常句柄 242

9.1.4 Linux异常程序流 243

9.2 中断原理 244

9.2.1 外部中断请求 244

9.2.2 Zynq - 7000 SoC内的中断环境 247

9.2.3 中断控制器的功能 248

9.3 Vivado环境下中断系统的实现 252

9.3.1 Cortex - A9处理器中断及异常初始化流程 252

9.3.2 Cortex - A9 GPIO控制器初始化流程 252

9.3.3 导出硬件设计到SDK 253

9.3.4 创建新的应用工程 253

9.3.5 运行应用工程 256

第 章 Cortex - A9定时器原理及实现 257

10.1 定时器系统架构 257

10.1.1 CPU私有定时器和看门狗定时器 257

10.1.2 全局定时器计数器 258

10.1.3 系统级看门狗定时器 259

10.1.4 3重定时器计数器 261

10.1.5 IO信号 264

10.2 Vivado环境下定时器的控制实现 264

10.2.1 打开前面的设计工程 265

10.2.2 创建SDK软件工程 265

10.2.3 运行软件应用工程 267

第 章 Cortex - A9 DMA控制器原理及实现 268

11.1 DMA控制器架构 268

11.2 DMA控制器功能 271

11.2.1 考虑AXI交易的因素 272

11.2.2 DMA管理器 273

11.2.3 多通道数据FIFO(MFIFO) 274

11.2.4 存储器存储器交易 274

11.2.5 PL外设AXI交易 274

11.2.6 PL外设请求接口 275

11.2.7 PL外设长度管理 276

11.2.8 DMAC长度管理 277

11.2.9 事件和中断 278

11.2.10 异常终止 278

11.2.11 安全性 280

11.2.12 IP配置选项 282

11.3 DMA控制器编程指南 282

11.3.1 启动控制器 282

11.3.2 执行DMA传输 282

11.3.3 中断服务例程 282

11.3.4 寄存器描述 283

11.4 DMA引擎编程指南 284

11.4.1 写微代码编程用于AXI交易的CCRx 284

11.4.2 存储器到存储器传输 284

11.4.3 PL外设DMA传输长度管理 287

11.4.4 使用一个事件重新启动DMA通道 289

11.4.5 中断一个处理器 289

11.4.6 指令集参考 290

11.5 编程限制 291

11.6 系统功能之控制器复位配置 292

11.7 IO接口 293

11.7.1 AXI主接口 293

11.7.2 外设请求接口 293

11.8 Vivado环境下DMA传输的实现 294

11.8.1 DMA控制器初始化流程 295

11.8.2 中断控制器初始化流程 295

11.8.3 中断服务句柄处理流程 296

11.8.4 导出硬件设计到SDK 296

11.8.5 创建新的应用工程 297

11.8.6 运行软件应用工程 303

第 章 Cortex - A9安全性扩展 305

12.1 TrustZone硬件架构 305

12.1.1 多核系统的安全性扩展 307

12.1.2 普通世界和安全世界的交互 307

12.2 Zynq - 7000 APU内的TrustZone 308

12.2.1 CPU安全过渡 309

12.2.2 CP15寄存器访问控制 310

12.2.3 MMU安全性 310

12.2.4 L1缓存安全性 311

12.2.5 安全异常控制 311

12.2.6 CPU调试TrustZone访问控制 311

12.2.7 SCU寄存器访问控制 312

|

| 內容試閱:

|

前言

本书是在作者已经出版的《Xilinx Zynq-7000嵌入式系统设计与实现:基于ARM Cortex-A9双核处理器和Vivado的设计方法》一书基础上修订而成。主要修订内容包括:

(1)删除原书第一章Zynq-7000 SoC的Vivado设计流程一节的内容,增加了Arm架构与分类一节的内容,系统介绍了Arm架构与不同处理器IP之间的关系,使得读者能更加系统了解并掌握Arm架构与Cortex-M、Cortex-R和Cotex-A框架下不同处理器IP之间的对应关系。

(2)本书增加了第30章,该章主要介绍了PetaLinx 2018.2工具,以及通过该工具在Xilinx SoC器件上构建Ubuntu操作系统环境的方法。需要指出,与本书前面使用传统的方法搭建Ubuntu操作系统环境相比,通过Xilinx公司自己的PetaLinx工具,使得在Xilinx Zynq-7000 SoC以及在UltraScale MPSoC上搭建Ubuntu操作系统环境更加便捷高效,显著降低了构建操作系统运行环境的难度,更加有利于初学者的入门学习。

(3)作为本书的亮点之一,在使用PetaLinx工具构建嵌入式操作系统运行环境的基础上,构建了嵌入式Python语言开发环境,并在所构建的环境下使用Python语言开发了应用程序。为了比较Python语言在arm Cortex-A9嵌入式处理器上的运行性能,同时在PC笔记本电脑上也构建了Python语言开发环境,并使用Python语言开发了应用程序。因此,实现了Zynq-7000 SoC作为服务器,以及PC笔记本电脑作为客户端的网络交互和数据传输功能。

(4)修改并更正了书中的一些错误。

考虑到Vivdo集成开发环境的主要功能和开发界面没有明显的不同,因此,书中所有案例仍然保留原来的开发版本。但是,增加的一章内容使用了较新的PetaLinux 2018.2环境。

总体来说,通过本书这一次的修订,使得介绍嵌入式系统设计的内容更加条理化,读者更加容易系统学习基于Arm Cortex-A9处理器的嵌入式系统硬件和软件设计方法,进一步降低了学习Arm嵌入式系统和Xilinx Zynq-7000 SoC的难度。

由于作者水平有限,书中难免有不足之处,恳请读者批评指正,以帮助读者今后进一步提高图书的编写质量。同时,也要感谢电子工业出版社的张迪编辑为本书的出版所做出的辛勤工作,也要感谢作者曾经带过并且已经毕业的研究生张艳辉,协助作者修订了本书,使得作者可以将更加精彩的内容奉献给国内广大的读者。

作者

2019.09于北京

|

|