新書推薦:

《

山河不足重,重在遇知己

》

售價:NT$

252.0

《

独自走过悲喜

》

售價:NT$

381.0

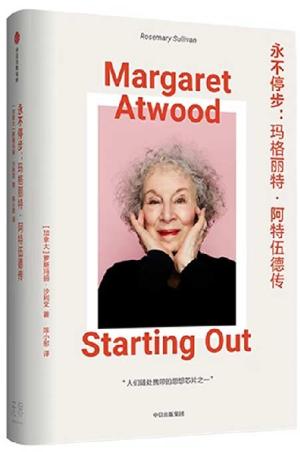

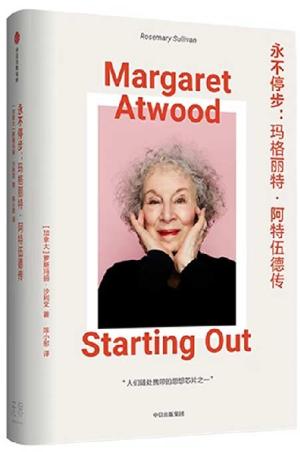

《

永不停步:玛格丽特·阿特伍德传

》

售價:NT$

442.0

《

假努力:方向不对,一切白费

》

售價:NT$

335.0

《

北京三万里

》

售價:NT$

437.0

《

争吵的恋人:我们为什么相爱,又为什么争吵

》

售價:NT$

330.0

《

秘史:英国情报机构的崛起

》

售價:NT$

381.0

《

李鸿章及其时代:中西方世界的历史撞击

》

售價:NT$

330.0

|

| 內容簡介: |

|

孟宪元、陈彰林、陆佳华编著的《Xilinx新一代FPGA设计套件Vivado应用指南》系统论述了新一代FPGA设计套件Vivado的性能、使用方法以及FPGA的开发方法。全书内容包括Vivado设计套件的特性,全面可编程FPGA器件的架构,使用Vivado套件创建复杂数字系统设计项目,仿真系统功能,RTL分析产生网表文件,性能要求的时序约束及综合,布局布线及静态时序分析和生成位流文件等全部设计过程,基于项目和非项目批作业两种用Tcl指令的设计模式,同步设计技术、HDL编码技术、时序收敛和HLS优化DSP算法等关键技术,并以实例介绍了嵌入式系统的设计方法等。本书适合作为高校电子信息类专业的实践教学用书和工程技术人员的参考用书。

|

| 目錄:

|

第1章 Vivado设计套件

1.1 单一的、共享的、可扩展的数据模型

1.2 标准化XDC约束文件——SDC

1.3 多维度解析布局器

1.4 IP 封装器、集成器和目录

1.5 Vivado HLS把ESL带入主流

1.6 其他特性

1.6.1 快速的时序收敛

1.6.2 提高器件利用率

1.6.3 增量设计技术

1.6.4 Tcl特性

1.7 Vivado按键流程执行设计项目

1.7.1 KC705开发板实现计数器

1.7.2 在Nexys4开发板实现计数器

第2章 7系列FPGA架构和特性

2.1 7系列结构特点

2.1.1 采用统一的 7 系列架构

2.1.2 高性能和低功耗结合的工艺

2.2 扩展7系列的UltraScale架构

2.3 可配置逻辑模块CLB

2.3.1 Slice的结构和功能

2.3.2 SliceM配置为SRL

2.3.3 SliceM配置为分布式RAM

2.4 7系列专用模块: Block RAMFIFO和DSP模块

2.4.1 Block RAMFIFO

2.4.2 DSP模块

2.4.3 IO模块

2.4.4 时钟资源

2.5 由RTL代码推论实验

2.5.1 计数器程序

2.5.2 实验结果

第3章 创建设计项目

3.1 wave_gen设计概述

3.2 启动Vivado

3.3 仿真设计

3.3.1 添加仿真需要的信号

3.3.2 运行仿真和分析仿真结果

3.4 利用时钟向导配置时钟子系统

3.5 产生IP集成器子系统设计

3.5.1 产生IP集成器模块设计

3.5.2 定制IP

3.5.3 完成子系统设计

3.5.4 产生IP输出产品

3.5.5 例示IP到设计中

第4章 RTL级分析和设计网表文件

4.1 网表文件

4.1.1 设计项目数据库

4.1.2 网表文件

4.1.3 推演的设计网表文件

4.1.4 综合的设计网表文件

4.1.5 实现的设计网表文件

4.2 RTL设计分析

4.2.1 RTL网表文件

4.2.2 RTL设计规则校验

4.2.3 浏览设计的层次

4.2.4 平面规划布图

4.2.5 时钟规划布图

4.3 网表文件的设计对象

4.3.1 通过get_*命令来寻找网表中的对象

4.3.2 设计层次

4.3.3 pin的层次与名称

4.3.4 层次展平化

4.3.5 Nets的层次分段

4.4 设计对象特性

4.4.1 查看对象的特性

4.4.2 Cell的特性

4.4.3 Port的特性

4.4.4 Pin的特性

4.4.5 用户自定义特性

4.4.6 使用特性过滤对象

4.5 对象连通性

4.5.1 层次结构下get_pins命令的使用

4.5.2 GUI的使用

4.5.3 图形化帮助界面

4.6 RTL分析实例

本章小结

第5章 设计综合和基本时序约束

第6章 设计实现与静态时序分析

第7章 Tcl命令设计项目

第8章 同步设计技术

第9章 HDL编码技巧

第10章 时序收敛

第11章 硬件诊断

第12章 Vivado HLS

第13章 嵌入式系统Zynq设计

|

|